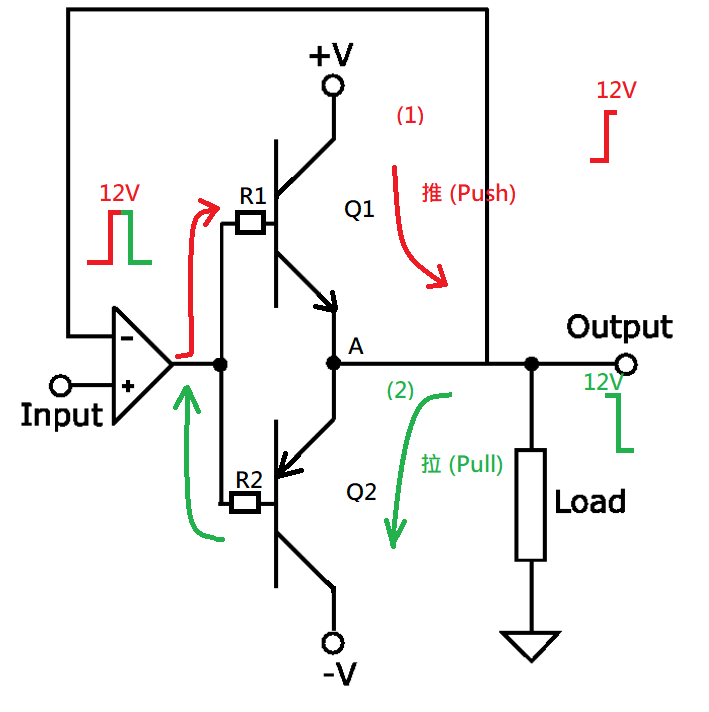

今天來說明推挽電路 (push-pull circuit) 的原理,筆者認為改為"推拉電路"更為貼切! 其結構為兩個不同 type 的電晶體串接 (p-type, n-type),以下為上P下N的推挽電路:

這個電路用到兩個電晶體 (Q1:npn, Q2:pnp),其基極 (base) 再各自串接兩個限流電阻(假設皆為 4.7k),最前方兩端連接在一起,為信號輸入端,兩個電晶體的射極 (emitter) 各自連接在一起為輸出。當信號輸入為 high 時 (假設為 5V),上面電晶體(Q1)導通,下面電晶體(Q2)關閉,因為上面電晶體 (Q1) 的 VBE(base-emitter voltage difference) 為 0.7V,所以,此時 A 點為 4.3V,但 Q2 的信號輸入端 base 為 5V (逆偏,因為 Q2 (npn) 的 emitter 電位(VE)必須高於 base (VB)才能導通),因此,下面電晶體(Q2)關閉。此時,電流由 Q1 的集極 ( collector) 流向射極 (emitter),再經由 output 出去,是為"推" (push)。

當輸入端為 low 時 (假設為 0V),Q1 關閉,此時,Q2 的 emitter (VE) 比 base (VB)高於 0.7V 以上,因此,電晶體導通; 此時,A 點的電壓相當於 0V,因此,電流由 output 負載端流向電晶體 Q2,是為"挽" (pull)。

所以,也就造成輸入高電位時,上方的電晶體導通,下方的電晶體關閉; 當輸入為低電位時,上方的電晶體關閉,下方的電晶體就導通 (高上開,低下開) 那你一定有疑問,如果當輸入波形稍微失真,不是理想的方波時,會不會造成 Q1 和 Q2 同時導通 (會造成電路燒毀!)嗎? 答案是不會的! 由以上文章可知,上P下N的結構,由於 BJT 電晶體的特性,高電壓時上面導通,下面無法被驅動,因此關閉; 而當低電位時,上方電晶體無法被驅動,下方電晶體導通; 即便波形有點失真,導通電晶體(Q1 和 Q2)的電壓上下限區間無法重疊,因此無法同時導通!